#### <u>SP9 Neuromorphic Computing Platform</u> - Results from SGA2 Year 2 (D9.6.2 - SGA2)

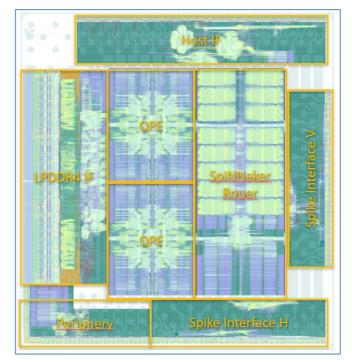

Figure 1: The BrainScaleS (upper image) and SpiNNaker (lower image) machines. These machines form the HBP Neuromorphic Computing Platform, offering accelerated learning and programmable flexibility respectively.

| Project Number:        | 785907                                                                                                                                                                                                                                                                                                                                                                                                        | Project Title:         | Human Brain Project SGA2 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|

| Document Title:        | SP9 Neuromorphic Computing Platform - Results from SGA2 year 2                                                                                                                                                                                                                                                                                                                                                |                        |                          |

| Document Filename:     | D9.6.2 (D62.2 D47) SGA2 M2                                                                                                                                                                                                                                                                                                                                                                                    | 4 ACCEPTED 200731.docx | (                        |

| Deliverable Number:    | SGA2 D9.6.2 (D62.2, D47)                                                                                                                                                                                                                                                                                                                                                                                      |                        |                          |

| Deliverable Type:      | Report                                                                                                                                                                                                                                                                                                                                                                                                        |                        |                          |

| Work Packages:         | WP9.1 - WP 9.6                                                                                                                                                                                                                                                                                                                                                                                                |                        |                          |

| Key Result(s):         | KR9.1 - KR9.6, KR9.x                                                                                                                                                                                                                                                                                                                                                                                          |                        |                          |

| Dissemination Level:   | PU = Public                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                          |

| Planned Delivery Date: | SGA2 M24 /31 Mar 2020                                                                                                                                                                                                                                                                                                                                                                                         |                        |                          |

| Actual Delivery Date:  | SGA2 M25 / 06 Apr 2020; Accepted 31 Jul 2020                                                                                                                                                                                                                                                                                                                                                                  |                        |                          |

| Author(s):             | SP9 members                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                          |

| Compiled by:           | Steve FURBER, UMAN (P63)                                                                                                                                                                                                                                                                                                                                                                                      |                        |                          |

| Contributor(s):        | SP9 members                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                          |

| SciTechCoord Review:   | Mehdi SNENE, EPFL (P1)                                                                                                                                                                                                                                                                                                                                                                                        |                        |                          |

| Editorial Review:      | Guy WILLIS, EPFL (P1)                                                                                                                                                                                                                                                                                                                                                                                         |                        |                          |

| Description in GA:     | The summary of SP 9 results for project months M13-24, broken down by task. WPs involved: WP9.1, WP9.2, WP9.3, WP9.4, WP9.5 and WP9.6<br>In order to report fully, the Deliverable may need to include information that the SP does not wish to make public at the time of the report. This material will be included in the Deliverable for the EC and Reviewers, but not in the version published publicly. |                        |                          |

| Abstract:              | This Deliverable describes progress over the second 12 months of SGA2 (April 2019 - March 2020) in the development of the Neuromorphic Computing Platform.                                                                                                                                                                                                                                                    |                        |                          |

| Keywords:              | Neuromorphic computing, SpiNNaker, SpiNNaker-2, BrainScaleS, BrainScaleS-2,<br>Theory                                                                                                                                                                                                                                                                                                                         |                        |                          |

| Target Users/Readers:  | Scientists interested in neuromorphic computing                                                                                                                                                                                                                                                                                                                                                               |                        |                          |

| 1. | Overview   |                                                                                                                           | 6    |

|----|------------|---------------------------------------------------------------------------------------------------------------------------|------|

| 2  | Introducti | on                                                                                                                        | 7    |

| 3. | Key Resul  | t KR9.1: Both first-generation machines integrated into joint platform                                                    | 8    |

|    | 3.1 Outpu  | uts                                                                                                                       |      |

|    | 3.1.1      | Overview of Outputs                                                                                                       | 8    |

|    | 3.1.2      | Output 1                                                                                                                  | 8    |

|    | 3.1.3      | Output 2: SpiNNaker related                                                                                               | 9    |

|    | 3.1.4      | Output 3: BrainScaleS-1 related                                                                                           | 9    |

|    | 3.2 Valida | ation and Impact                                                                                                          |      |

|    | 3.2.1      | Actual and Potential Use of Output(s)                                                                                     | .10  |

| 4. | Key Resul  | t KR9.2: Comprehensive software suite for the operation of neuromorphic machines.                                         | 11   |

|    | 4.1 Outpu  | ıts                                                                                                                       | . 11 |

|    | 4.1.1      | Overview of Outputs                                                                                                       | . 11 |

|    | 4.1.2      | Output 1: Multicompartmental models in PyNN                                                                               | . 12 |

|    | 4.1.3      | Output 2: SpiNNaker Neuromorphic Computing System                                                                         | . 12 |

|    | 4.1.4      | Output 3: App for machine-learning with neuromorphic hardware                                                             | .13  |

|    | 4.1.5      | Output 4: MPI-SpiNNaker                                                                                                   | .14  |

|    | 4.1.6      | Output 5: Neuromorphic Benchmarks                                                                                         | . 15 |

|    | 4.1.7      | Output 6: MUSIC library                                                                                                   | .16  |

|    | 4.1.8      | Output 7: Hardware integration                                                                                            | .16  |

|    | 4.1.9      | Output 8: CSA library                                                                                                     | . 16 |

|    | 4.1.10     | Output 9: BrainScaleS-1 Software                                                                                          | . 16 |

|    | 4.1.11     | Output 10: BrainScaleS-2 Software                                                                                         | .17  |

|    | 4.2 Valida | ation and Impact                                                                                                          | . 18 |

|    | 4.2.1      | Actual and Potential Use of Output(s)                                                                                     | . 18 |

|    | 4.2.2      | Publications                                                                                                              | . 19 |

| 5. |            | t KR9.3 Operational prototype of a second generation BrainScaleS chip featuring on-c                                      |      |

|    |            | icity and non-linear dendritic processing                                                                                 |      |

|    | 5.1 Outpu  | ıts                                                                                                                       |      |

|    | 5.1.1      | Overview of Outputs                                                                                                       | . 19 |

|    | 5.1.2      | Output 1: Deep learning with time-to-first-spike coding                                                                   |      |

|    | 5.1.3      | Output 2: Sampling-based Bayesian computation                                                                             |      |

|    | 5.1.4      | Output 3: Structural plasticity                                                                                           |      |

|    | 5.1.5      | Output 4: Control of criticality and computation                                                                          |      |

|    | 5.1.6      | Output 5: Insect-inspired navigation                                                                                      | . 22 |

|    | 5.1.7      | Output 6: Spiking Heidelberg Digits                                                                                       | . 23 |

|    | 5.1.8      | Output 7: BrainScaleS-2 setups                                                                                            | . 23 |

|    | 5.2 Valida | ation and Impact                                                                                                          |      |

|    | 5.2.1      | Actual and Potential Use of Output(s)                                                                                     | .24  |

|    | 5.2.2      | Publications                                                                                                              |      |

| 6  |            | t KR9.4: Operational prototype of a second generation SpiNNaker chip featuring 10-f                                       |      |

|    | -          | energy efficiency, 144 Cortex M4F and 36 GIPS/Watt per chip                                                               |      |

|    | •          | uts                                                                                                                       |      |

|    | 6.1.1      | Overview of Outputs                                                                                                       |      |

|    | 6.1.2      | Output 1: SpiNNaker next generation chip                                                                                  |      |

|    |            | ation and Impact                                                                                                          |      |

|    | 6.2.1      | Actual and Potential Use of Output(s)                                                                                     |      |

|    | 6.2.2      | Publications                                                                                                              |      |

| 7. | network l  | It KR9.5 Two novel theories of computational principles: Learning-to-learn (L2L) a earning based on dendritic computation | 27   |

|    | 7.1 Outpu  | uts                                                                                                                       |      |

|    | 7.1.1      | Overview of Outputs                                                                                                       | . 27 |

|    |            |                                                                                                                           |      |

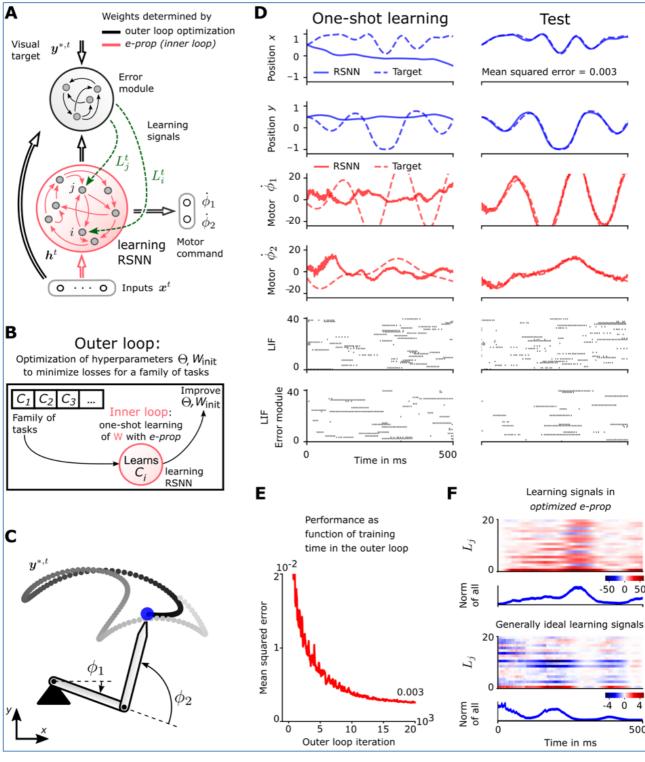

| 7.1.2          | Output 1: Learning-to-learn (L2L) applied to e-prop                                   | 28   |

|----------------|---------------------------------------------------------------------------------------|------|

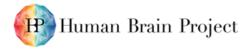

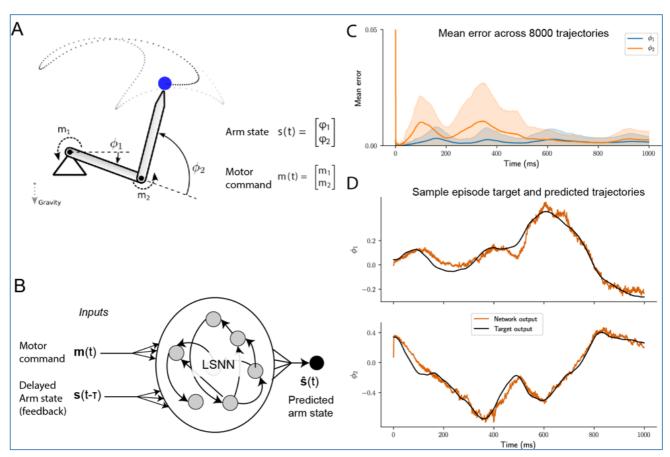

| 7.1.3          | Output 2: Application of L2L to Reservoir Computing:                                  | 29   |

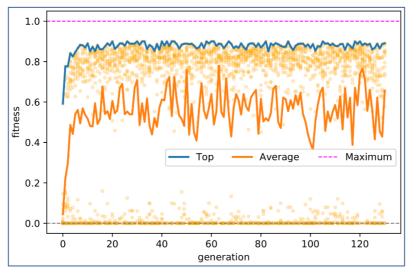

| 7.1.4          | Output 3: L2L for robotics                                                            | 30   |

| 7.1.5          | Output 4: Network learning based on dendritic computation                             | 31   |

| 7.2 Valio      | dation and Impact                                                                     | 31   |

| 7.2.1          | Actual and Potential Use of Output(s)                                                 | 31   |

| 7.2.2          | Publications                                                                          | 31   |

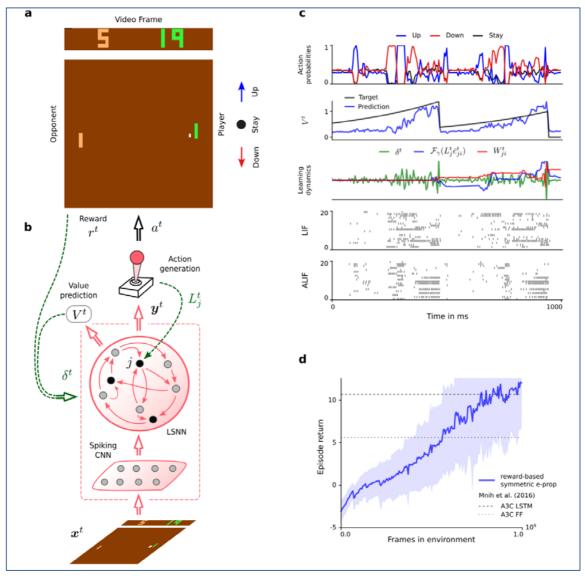

| 8. Key Resu    | It KR9.6: Applications exploiting the new features of second generation systems       | 32   |

| 8.1 Outp       | buts                                                                                  | 32   |

| 8.1.1          | Overview of Outputs                                                                   | 32   |

| 8.1.2          | Output 1 - Mapping DNNs on SpiNNaker2                                                 | 32   |

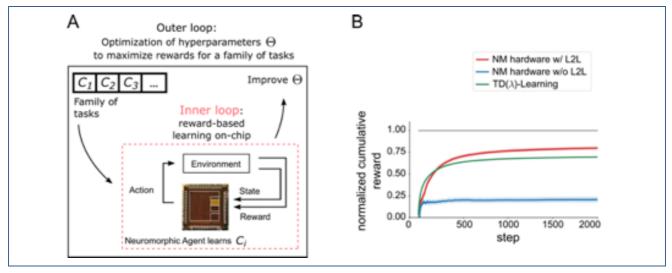

| 8.1.3          | Output 2 - Learning-to-Learn (L2L) applied to reinforcement learning on BrainScaleS   | 33   |

| 8.1.4          | Output 3 - BrainScaleS applications                                                   | 33   |

| 8.1.5          | Output 4 - Structural plasticity on BrainScaleS-2                                     | 34   |

| 8.2 Valio      | dation and Impact                                                                     | 34   |

| 8.2.1          | Actual and Potential Use of Output(s)                                                 |      |

| 8.2.2          | Publications                                                                          | 34   |

| 9. KR9.x: R    | esults by SP9 not under the KR9.1-6                                                   | . 35 |

|                | outs                                                                                  |      |

| 9.1.1          | Overview of Outputs                                                                   |      |

| 9.1.2          | Output 1: Use-cases                                                                   | 35   |

| 9.1.3          | Output 2: Continuously running the first generation SpiNNaker and BrainScaleS machine |      |

| 9.1.4          | Output 3: Embedded next generation wafers                                             |      |

| 9.1.5          | Output 4: NEAL Components and Agents                                                  |      |

| 9.1.6          | Output 5: L2L system for few shot object recognition                                  |      |

| 9.1.7          | Output 6 - Event-based electronic olfaction with SpiNNaker                            |      |

| 9.1.8          | Output 7: Additional theory advances                                                  |      |

|                | dation and Impact                                                                     |      |

| 9.2.1          | Actual and Potential Use of Output(s)                                                 |      |

| 9.2.2          | Publications                                                                          |      |

|                | sults: links to KRc5.1, KRc5.2, KRc5.3 and KRc5.4 in Deliverable D9.4.2 (TODO:        |      |

| 11. Conclusion | on and Outlook (max 1,200 words)                                                      | . 44 |

#### Table of Tables

| Table 1: SpiNNake-2  | prototype performance. | compared to SpiNNaker-1 |    |

|----------------------|------------------------|-------------------------|----|

| rabio il opininano E | prototypo porrormanoo, | oomparoa to opininantoi | 20 |

#### Table of Figures

| Figure 1: The BrainScaleS (upper image) and SpiNNaker (lower image) machines                     | 1  |

|--------------------------------------------------------------------------------------------------|----|

| Figure 2: App for graphical neuromorphic model building                                          | 13 |

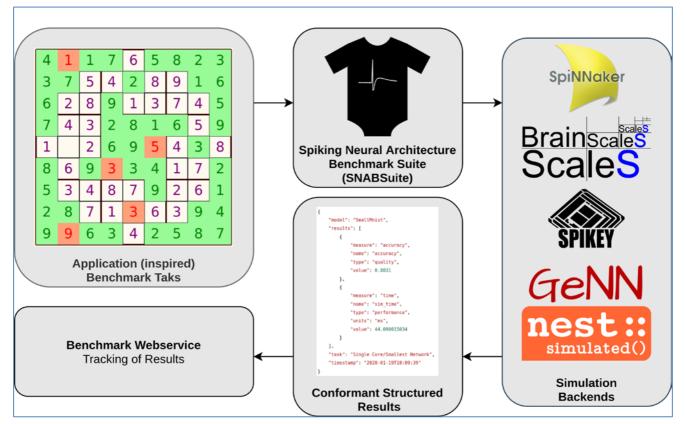

| Figure 3: Benchmark work-flow: from an application to the tracking of results in the web-service | 15 |

| Figure 4: Feed-forward network for fast inference                                                | 20 |

| Figure 5: Network of LIF neurons for Bayesian inference                                          | 21 |

| Figure 6: Structural plasticity on BrainScaleS-2                                                 | 21 |

| Figure 7: Influence of criticality on task performance                                           | 21 |

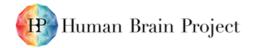

| Figure 8: Virtual insectoid agent on BrainScaleS-2                                               | 22 |

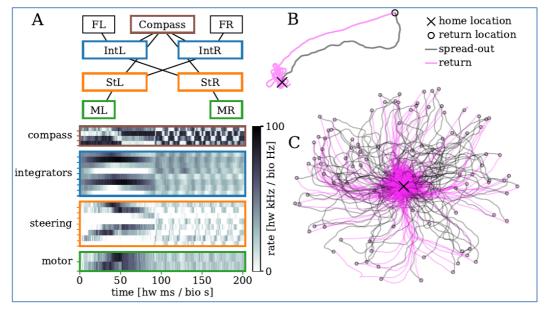

| Figure 9: Representation of the Spoken digits dataset                                            | 23 |

| Figure 10: BrainScaleS-2 HICANN-X setup                                                          | 23 |

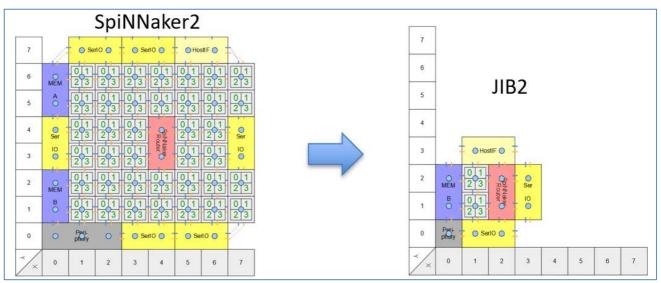

| Figure 11: Testchip JIB2                                                                         | 25 |

| Figure 12: Tape-out ready layout of the JIB2 testchip                                            | 26 |

| Figure 13: Scheme and performance of L2L with e-prop                                             | 29 |

| Figure 14: Learning-to-learn a nonlinear transformation of a time series                         | 30 |

| Figure 15: Learning-to-learn for a simple robotic arm:                                           | 31 |

## 1. Overview

The SP9 Neuromorphic Computing Platform is part of the Human Brain Project's EBRAINS research infrastructure, offering open access to two of the world's leading neuromorphic (brain-inspired) computing systems. SpiNNaker (Spiking Neural Network Architecture) is a many-core digital computer incorporating a million ARM processor cores, and is the world's largest neuromorphic computing system. BrainScaleS employs physical emulation, wherein analogue electronic circuits model the equations of the biological components directly, and is the world's fastest neuromorphic computing system. Together, these two systems form the EBRAINS Neuromorphic Computing Platform and, as such, are the world's only openly accessible neuromorphic computing resources.

Significant advances over the last 12 months of SGA2 included the demonstration on SpiNNaker of the first robust, real-time implementation of the cortical microcircuit, paving the way for a real-time multi-area cortical model in SGA3, published in the Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences, in December 2019. The development of a range of novel learning algorithms on the BrainScaleS-2 prototype chip are also noteworthy. SP9 has, with CDP5, contributed to the development of novel theories of computational principles, including learning-to-learn (L2L) and learning based upon dendritic computation, both of which are broadly applicable to neuromorphic systems. A gradient descent algorithm, e-prop, promises to bring the capabilities of backpropagation in artificial neural networks to spiking neural networks in a biologically-plausible mechanism, opening up the prospect of the wider applicability of spiking networks to industrially-relevant applications. All of these novel learning algorithms will be developed and applied to the Neuromorphic Computing Platform during SGA3.

## 2. Introduction

During the two years of SGA2, the field of neuromorphic computing received increased attention; in particular, with the growing presence of the Intel Loihi chip across the academic research community. Loihi is not a full product, so companies cannot build product plans around it; rather, it is a "research prototype", available to the academic community, which Intel is using to explore the future potential of such a product.

Over the same period, there has been a growing expectation that neuromorphic technology has something to offer in the commercial AI domain, perhaps by reducing the very high power demands of conventional artificial neural network (ANN) solutions. Event-based AI, or bio-AI, has intrinsic properties that, when correctly realised, offer the prospect of significant power reduction, though there are still challenges in delivering this advantage. Training ANNs is now highly developed through frameworks such as Tensorflow and Keras, so one approach is to train an ANN and then convert it into a spiking neural network (SNN) for the inference phase. However, the simplest conversion approach, which is to use rate-based encoding, where the firing rate of an SNN neuron corresponds to the activation output of the ANN neuron, to replace a digital multiplication with multiplication by repeated addition, and confers no fundamental advantage. To show an advantage, the SNN must use an encoding other than rate-based, and some interesting alternatives are just beginning to emerge from work carried out in SP9. Key Result KR9.6 reports on applications developed after M12 that exploit the 2<sup>nd</sup>-generation features of the hardware platforms. These applications include tools for mapping deep networks on SpiNNaker-2, hyper-parameter optimisation, structural plasticity, Bayesian sampling and others that are relevant for potential applications of HBP hardware in Artificial Intelligence.

Of course, the major focus of SP9 is on developing neuromorphic computing systems that contribute to brain science through the EBRAINS infrastructure. Here there has been solid progress over the last 12 months of SGA2 in improving the stability and capabilities of the supporting software stacks, and this has been demonstrated in the speeding up the cortical microcircuit model on SpiNNaker, from a 20x slow-down when reported in May 2018 to real-time in December 2019. Parallel advances on BrainScaleS have demonstrated a suite of novel learning algorithms.

# 3. Key Result KR9.1: Both first-generation machines integrated into Joint Platform

### 3.1 Outputs

#### 3.1.1 Overview of Outputs

#### 3.1.1.1 List of Outputs contributing to this KR

- Output 1: Neuromorphic Computing Platform Remote Access Service (C3042)

- Output 2: SpiNNaker Neuromorphic Computing System (C2)

- Output 3: BrainScaleS-1 (C1)

#### 3.1.1.2 How Outputs relate to each other and the Key Result

Output 1 is used to submit jobs to and extract results from Output 2 and Output 3. Outputs 2 and 3 are the first generation machines (namely SpiNNaker and BrainScaleS respectively) which are integrated into the Joint Platform as part of this KR.

#### 3.1.2 Output 1

The Neuromorphic Computing Platform Remote Access Service (C3042) enables users to run simulations/emulations on the BrainScaleS, SpiNNaker and Spikey systems by submitting jobs to a central queue, and then retrieving the results once the simulation is complete. The core of the service is a web service with a REST API (C344), with authentication using the HBP identity service. Users can submit jobs using a Collaboratory app (Job Manager app; C343), through a Python client (C345), or on the command line (part of C345). The service also has a number of other components, such as a job statistics dashboard (C371) and a resource/quota management service (C369, C370).

In the last year, the Job Manager app has had a number of minor improvements, but the major advancements have been in the back end. We have deployed a service for load-balancing and failover (C1638), to increase the availability of the REST API and Collaboratory apps. These services are currently running on two separate machines, using the ICEI VM infrastructure at CSCS. A load-balancing service routes requests alternately to the two servers, and detects if one of the servers is not responding (in which case, a monitoring service alerts the platform maintainers). We have also developed Knowledge Graph (KG) schemas, based on the W3C PROV standard, for neuromorphic simulations, models, and results (C377), and periodically synchronise the job database with the KG, so that neuromorphic workflows can be fully integrated with other tools available on the HBP/EBRAINS infrastructure. We are in the process of rewriting the REST API to communicate directly with the KG, avoiding the need for the periodic synchronisation.

#### Progress vs State of the Art & Recent Developments

The criterion for "beyond state of the art" for SGA2 is "Worldwide unique integration of neuromorphic computing machines into the HBP-JP". We consider that this criterion has been satisfied.

| Component                   | Link to                    | URL                                                                                                                            |

|-----------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| C3042 - SP9<br>Neuromorphic | Software Repository        | https://github.com/HumanBrainProject/hbp_neuromorphic_platform<br>https://github.com/HumanBrainProject/hbp-neuromorphic-client |

| Computing                   | Technical<br>Documentation | https://www.hbpneuromorphic.eu/developer_guide/index.html                                                                      |

D9.6.2 (D62.2 D47) SGA2 M24 ACCEPTED 200731.docx PU = Public 30-Sep-2020 Page 8 / 44

| Component                   | Link to            | URL                                                                                                                                                                                           |

|-----------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Remote<br>Access<br>Service | User Documentation | https://collab.humanbrainproject.eu/#/collab/51 (community account required. Request at: <u>neuromorphic@humanbrainproject.eu</u> )<br>https://electronicvisions.github.io/hbp-sp9-guidebook/ |

#### 3.1.3 Output 2: SpiNNaker related

The SpiNNaker machine continues to be accessible from the Joint Platform via Output 1. The service has been updated to reduce the turnaround time when accessing jobs via the Joint Platform, by precloning the git modules required to operate the machine. These are then updated if required and any branch or tag changes are then made before the job is run.

The SpiNNaker machine has also been made available through Jupyter notebooks, which are authenticated using the HBP authentication service. This allows the users to make use of the SpiNNaker machine in a more interactive way. The SpiNNaker-Neurorobotics Platform (NRP) interface has also been deployed through these Jupyter notebooks, so users can start their own NRP instance on a host machine adjacent to the SpiNNaker machine.

| Component                             | Link to                    | URL                                                                                                                                                                                      |

|---------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | Software Repository        | https://github.com/SpiNNakerManchester/RemoteSpiNNaker                                                                                                                                   |

| C2 - SP9<br>SpiNNaker<br>Neuromorphic | Technical<br>Documentation | Integrated into code                                                                                                                                                                     |

| Computing                             | User Documentation         | https://collab.humanbrainproject.eu/#/collab/51 (community<br>account required. Request at: neuromorphic@humanbrainproject.eu)<br>https://electronicvisions.github.io/hbp-sp9-guidebook/ |

#### 3.1.4 Output 3: BrainScaleS-1 related

The BrainScaleS-1 has been accessible from the Joint Platform via Output 1. During the reporting period, its hardware and software infrastructure was completed and enhanced in several aspects, as described in the following paragraphs.

| Component    | Link to                 | URL                                                    |

|--------------|-------------------------|--------------------------------------------------------|

|              | Software Repositories   | https://github.com/electronicvisions/                  |

| Neuromorphic | Technical Documentation | Integrated into code and internal specification        |

|              |                         | https://electronicvisions.github.io/hbp-sp9-guidebook/ |

#### 3.1.4.1 Migration Raspberry Pi3/4

Updated BrainScaleS-1 systems are equipped with a newer version of Raspberry Pis, either with version 3B+ or 4. An upgrade-kit was developed for the existing systems. The software stack is updated to the newer version. The new Raspberry Pis have several advantages over the former ones. Now the Raspberry Pis boot over PXE and therefore don't need sd-cards anymore. Maintenance of the Raspbian Linux distribution used now is also easier and the BrainScaleS-1 monitor- and control-software is integrated in the continuous integration tool-chain. The Raspbian linux distribution has been upgraded too. The old one-core processor of the Raspberry Pi 1B was working at its limit. The new Raspberry Pis have additional CPU cores, which are useful for extensive monitoring features closer to the BrainScaleS-1 modules.

#### 3.1.4.2 Analysis of cooling concept of BrainScaleS-1

The cooling concept of the BrainScaleS-1 modules was analysed with regard to noise reduction, efficiency and power consumption. All of these aspects were improved by optimising air guidance through the module and exchanging selected fans, while keeping cooling performance equal. As a result, some of the fans could be slowed down to 50% of their full speed, which also reduced the noise level. The power consumption of all fans could be decreased from around 180W to 70W.

Additionally, a wafer temperature regulation system was developed. This pid regulator controls the fan speed to keep the wafer temperature constant at 48°C.

#### 3.1.4.3 Firmware Improvements for power supply boards

The power supply boards of the BrainScaleS-1 module received a new firmware. Calibration of sensor data on the boards returns a more accurate state of the system, in terms of current consumption and operating point of the analogue circuits. Furthermore, the stability increased as new protection routines were installed and this also reduced the number of repairs required. For example, a current shunt on one board would burn under certain conditions; this situation can now be detected in advance and handled. As a result, no repair has been required since the firmware update.

#### 3.1.4.4 Testing and integration of new wafer set

Wafer modules using wafers of the new HICANN v4.1 wafer set uncovered errors regarding communication with some HICANNs. To ensure that these errors were not introduced by the assembly procedure, a method for testing the wafers before the assembly had to be established. Therefore, an automated test suite for a wafer prober was developed and was used to test all components of the wafers of the new HICANN v4.1 wafer set. The tests that were integrated into the automated test suite covered High-Speed connection, slow control connection and power tests. Each type showed errors or irregularities at different HICANNs on each wafer in a low percentage range. These errors do not hinder wafer usage, but they do reduce the amount of resources that each wafer can provide.

The assembly process has started, using the wafers with the lowest error rates. Four wafers have been assembled and integrated into the BrainScaleS-1 system and this process is still ongoing.

## 3.1.4.5 Integration of new Analogue-to-Digital (ADC) subsystem into software framework

The communication layer for the ADC subsystem has been developed. It allows for configuration of the ADC front-ends, trigger sources and recording lengths for all channels. Additionally, aggregated and compressed data can be retrieved from SDRAM and are re-assembled into separate traces. The hardware abstraction layers required for integration into the current BSS-1 software stack are in development.

## 3.2 Validation and Impact

#### 3.2.1 Actual and Potential Use of Output(s)

Output 1 (Neuromorphic Computing Platform Remote Access Service):

The service is in use and provides an easy, installation free "first contact" with both NMC systems, directly integrated in the HBP Joint Platform Collaboratory. The service can also easily be used for training.

#### Output 2 SpiNNaker:

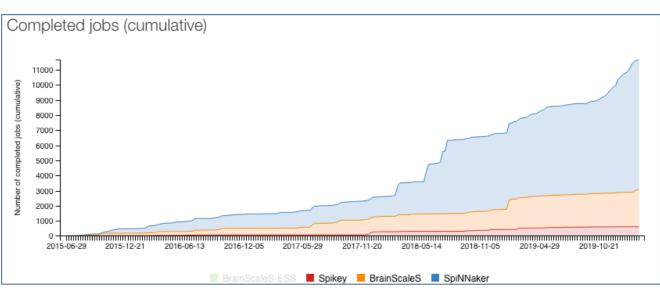

Users continue to use the SpiNNaker machine via the Joint Platform, with over 8,000 jobs in total completed to date (up from around 5,000 at the start of April 2019), submitted by 88 users (up from 69 at the start of April 2019). The SpiNNaker machine provides the HBP Research Infrastructure with a computing system capable of performing large-scale brain simulations, executed in real-time, allowing users to explore the performance of large-scale networks executing for longer durations. The Jupyter service has executed 14,660 runs, generated by 161 users, on the SpiNNaker machine since the service was started. Both the batch service and the Jupyter notebook service have been validated through continued interaction with users of the service, via the SpiNNaker mailing list and the HBP Support service.

#### Output 3 BrainScaleS-1:

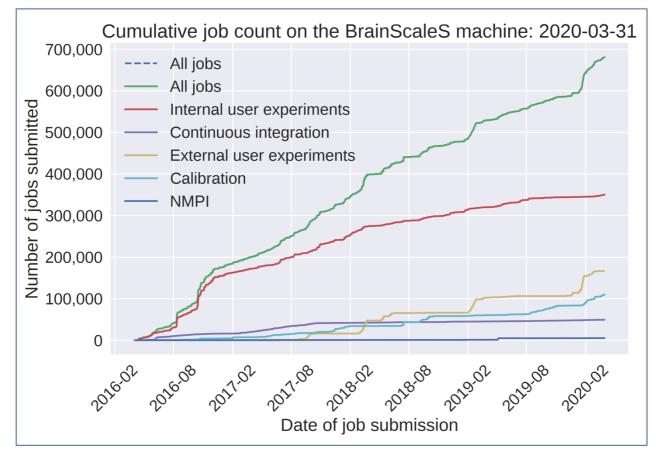

The BrainScaleS-1 platform has reached a state where it can demonstrate the feasibility of waferscale integration for neuromorphic computing, based on accelerated analogue physical models. In total, almost 400,000 jobs have been completed (c. 90,000 jobs since April 2019) by more than 70 users (40 users in the last 90 days). These numbers include jobs submitted via the collab interface, Jupyter, and the local batch submission system.

As soon as a wafer-scale version of the BrainScaleS-2 ASIC is available, the BrainScaleS platform will be capable of emulating the dynamics of learning and development of large networks of structured neurons in a time-continuous model, with an unprecedented energy efficiency.

The contributions of the individual tasks to the output are as follows:

The new Raspberry Pis improve the software maintainability and extend the possible monitoring and alerting options for the BrainScaleS-1 modules.

The cooling optimisations reduce the power consumption of the cooling system, which saves energy and costs, and expands the lifetime of components, because fans don't always run at full speed now.

The new power supply firmware reduced the number of repair actions.

The integration of the new HICANN v4.1 wafer set into the system increases the number of accessible chips with improved analogue neuromorphic circuitry.

The new ADC subsystem improves the readout capability and thus will allow faster and more accurate HICANN calibration results.

## 4. Key Result KR9.2: Comprehensive software suite for the operation of neuromorphic machines

#### 4.1 Outputs

#### 4.1.1 Overview of Outputs

#### 4.1.1.1 List of Outputs contributing to this KR

- Output 1: Multicompartmental models in PyNN (C349)

- Output 2: SpiNNaker Neuromorphic Computing System (C2)

- Output 3: App for machine-learning with neuromorphic hardware (C1656 & C1644)

- Output 4: MPI-SpiNNaker (C3045)

- Output 5: Neuromorphic Benchmarks (C2735)

- Output 6: MUSIC library (C347)

- Output 7: Hardware integration (C1810)

- Output 8: CSA library (C1769)

- Output 9: BrainScaleS-1 Software

- Output 10: BrainScaleS-2 Software

#### 4.1.1.2 How Outputs relate to each other and the Key Result

Output 2 provides the software for executing PyNN models on SpiNNaker. Currently, this has not been updated to work with Output 1.

Output 3 relies on Output 2 as one of its target platforms. New concepts introduced by Output 1 have been considered in the design, but cannot yet be deployed.

Output 5 relies on Output 2 and Output 9, as these are targeted by the benchmark suite. Improvements to those Outputs may improve benchmark results, and benchmarking may lead to improvements in the respective software stacks of the platforms.

#### 4.1.2 Output 1: Multi-compartmental models in PyNN

The next-generation BrainScaleS and SpiNNaker chips will allow multi-compartment neuron models, with non-linear mechanisms such as calcium dynamics. To support such models, work on extensions to PyNN began in SGA1 and continued in the first year of SGA2. In the second year of SGA2, we continued this work, adding support for the specific calcium and NMDA models that will be available in the BrainScaleS 2 chip (see Schemmel *et al.*, 2017; <u>https://arxiv.org/abs/1703.07286</u>).

| Component   | Link to                    | URL                                                            |

|-------------|----------------------------|----------------------------------------------------------------|

|             | Software Repository        | https://github.com/NeuralEnsemble/PyNN/tree/mc                 |

| C349 - PYNN | Technical<br>Documentation | https://neuralensemble.org/docs/PyNN/2.0/developers_guide.html |

|             | User Documentation         | https://neuralensemble.org/docs/PyNN/2.0/                      |

#### 4.1.3 Output 2: SpiNNaker Neuromorphic Computing System

The SpiNNaker software continues to be improved. A prototype has been written which allows the execution of the 1mm<sup>2</sup> cortical microcircuit to be executed in real time on the platform. Additionally, this network has been executed for 12 hours without any faults. We believe that this is the first time that this network has been run, both in real time and for such a duration, on any hardware, including HPC systems.

In addition, the software has been updated to run jobs that use even larger shares of the machine's resources, through the improvement of the routing table compression and routing key allocation algorithms. A network with around 8 million neurons and over 800 million synapses has been executed, using over 200 SpiNNaker boards.

The software development has concentrated on making the platform more stable, and on improving the documentation. To this end, the data-loading and extraction protocols have been refactored to ensure correct operation. The code documentation has been reviewed and completed where parts were missing.

The SpiNNaker platform is now considered to be at TRL6. This is demonstrated in four key areas that can be used to describe this TRL:

• Prototype implementations of the software demonstrated on full-scale realistic problems: The software can run the cortical microcircuit which has a realistic number of inputs, and a prototype exists for running this in real time. The software has also successfully run a neural network across over 200 SpiNNaker boards.

- Partially integrate with existing hardware/software systems: The software integrates with the latest version of PyNN and Neo. The SpiNNaker system has been integrated with the HBP Collaboratory and with Jupyter notebooks, and there is a proof-of-concept integration with the HBP neurorobotics platform. There have also been some successful runs of the SNNToolbox software with SpiNNaker. SpiNNaker has also been successfully used with real robots, including a basic integration with MiroBot and deeper integration with the TUM Pushbot.

- Limited documentation available: There is actually extensive documentation; including training documentation, in the form of installation instructions, lab manuals and presentations; hardware documentation, in the form of the chip datasheet and implemented protocol documentation; and user documentation, in the form of API-level documentation of the code.

- Engineering feasibility fully demonstrated: The large SpiNNaker machine has been built and successfully tested at different scales of operation. The software has also been shown to run large networks on the 1 million core machine.

| Component                 | Link to                 | URL                                                    |

|---------------------------|-------------------------|--------------------------------------------------------|

|                           | Software Repository     | https://github.com/SpiNNakerManchester/sPyNNaker8      |

| SpiNNaker<br>Neuromorphic | Technical Documentation | https://spinnaker8manchester.readthedocs.io/en/latest/ |

| Computing                 |                         | https://spinnakermanchester.github.io/                 |

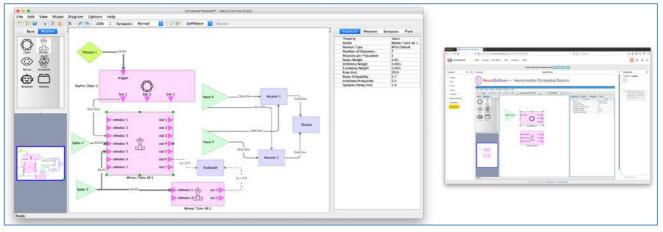

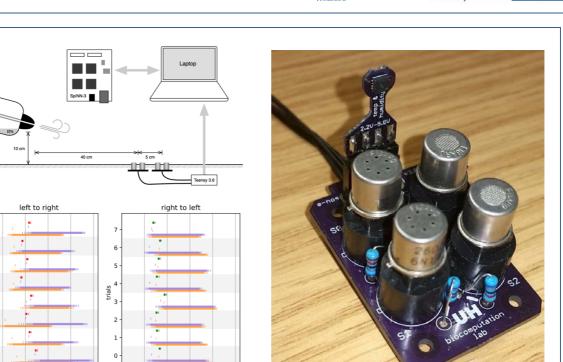

## 4.1.4 Output 3: App for machine-learning with neuromorphic hardware

The app for graphical neuromorphic model building (C1655) from SGA2 year one has been extended to support modular network components as an enabler for its practical use to describe larger machine-learning experiment set-ups (C1656). Modular components go beyond classical visual grouping of multiple network entities into a single node. Each module encapsulates expert knowledge about robust implementation techniques for typical subtasks on neuromorphic hardware. Only externally relevant neuron and synapse parameters are exposed in a consolidated inspector view. Coordinated sharing of consistent parameter sets in the module is expressed by the type concept for neurons and synapses in the underlying visual language. Module configuration in the editor includes scaling of the internal architecture and changes to the number of externally visible input or output ports.

The library of available composable modules (C1644) is provided as templates of ultimately PyNN-based generator functions for the module architecture. For example, the winner-take-all module provides a very universal sub-network, while the module for a head direction network is specific to the robotics domain. Beyond local installation of the app, deployment as a client-side web app inside the Collaboratory allows seamless remote access to the large-scale SP9 neuromorphic hardware platforms.

#### Figure 2: App for graphical neuromorphic model building

Local app inspecting the parameters of a winner-take-all module instance (left) and embedded collaboratory app (right)

#### Progress vs State of the Art & Recent Developments

Usage of a formally defined, typed visual language and structurally variable modules, with templatebased code generation, is an advance beyond existing graph editors for visual descriptions of network architectures.

| Component                                                                                                                 | Link to                    | URL                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------|

| C1656 - SP9 App for<br>machine-learning with<br>neuromorphic<br>hardware                                                  | Software<br>Repository     | https://github.com/hbp-unibi/NeuroCoCoon                                                           |

|                                                                                                                           | Technical<br>Documentation | https://github.com/hbp-<br>unibi/NeuroCoCoon/blob/master/Installation.md                           |

|                                                                                                                           | User<br>Documentation      | https://github.com/hbp-<br>unibi/NeuroCoCoon/blob/master/Usage.md                                  |

| C1644 -Library of<br>modular and<br>composable sub-<br>networks for<br>computing with<br>neuromorphic<br>hardware systems | Software<br>Repository     | https://github.com/hbp-<br>unibi/NeuroCoCoon/tree/master/ncc/src/de/unibi/hbp/ncc/lan<br>g/modules |

|                                                                                                                           | Technical<br>Documentation | https://github.com/hbp-<br>unibi/NeuroCoCoon/blob/master/Extending.md                              |

|                                                                                                                           | User<br>Documentation      | https://github.com/hbp-<br>unibi/NeuroCoCoon/blob/master/Usage.md                                  |

#### 4.1.5 Output 4: MPI-SpiNNaker

#### Flexible on-line reconfiguration and memory management system for SpiNNaker

The SpiNNaker neuromorphic architecture is increasingly used, not only for real-time simulation of brain-scale biological neural networks, but also to support innovative brain-inspired computational paradigms. In both domains, there is increasing demand for flexibility, in terms of network configuration and run-time redesign of network parameters and simulated neurons models. Due to the intrinsically high parallelism and complexity of the interconnected processing units, broadcasting updates to the cores is time consuming. Hence, static solutions, where the network is re-loaded from an external host, are highly inefficient. To address these requirements, we have designed the Application Command Protocol (ACP), which provides a mechanism to remotely trigger the execution of high-level op-codes by the cores and manage their application memory. We have demonstrated ACP in two SNN applications: i) SNN configuration, where simulation data are efficiently generated through ACP in the memory of computing nodes and ii) SNN reconfiguration, where ACP is used to change SNN network parameters at runtime and to easily switch from learning to test phase in a SNN classification application. The ACP protocol enabled a more flexible computational model and memory management system.

#### Message Passing Interface Component for SpiNNaker

Several studies have shown that neuromorphic platforms allow flexible and efficient simulations of SNN by exploiting the efficient communication infrastructure optimised for transmitting small packets across the many cores of the platform. However, the effectiveness of neuromorphic platforms in executing massively parallel general-purpose algorithms, while promising, is still to be explored. In the case of SpiNNaker, the implementation of MPI must deal with a resource limit, both in terms of memory and computing power. However, it can take advantage of the technology offered by on-chip routers, thereby obtaining efficient communication. The MPI-SpiNNaker software stack creates a simple working framework, offering a universally known programming model capable of making the SpiNNaker architecture available for a wide range of applications, both synchronous and asynchronous. (Benchmark in Urgese *et al.* 2019)

| Component | Link to                 | URL                                                                                                      |  |

|-----------|-------------------------|----------------------------------------------------------------------------------------------------------|--|

| C3045     | Software Repository     | https://github.com/neuromorphic-polito/SpinACP.git<br>https://github.com/neuromorphic-polito/SpinMPI.git |  |

|           | Technical Documentation |                                                                                                          |  |

User Documentation

#### 4.1.6 Output 5: Neuromorphic Benchmarks

In the second half of SGA2, the black-box benchmark framework SNABSuite (C2735) was extended to support more application driven benchmarks. Most notably, the framework now includes benchmarks on solving constraint satisfaction problems with the help of winner-take-all architectures (Ostrau *et al.*, 2019), classification benchmarks on the MNIST hand-written digits dataset, and central parts of a simultaneous localisation and mapping algorithm. The coupling to BrainScaleS has been improved, increasing the efficiency of the evaluation and utilising more features of the software stack. Furthermore, all benchmarks can be executed on Nvidia GPUs using the GeNN code-generation framework. The target TRL 6 has been reached, as a full software pipeline has been set into place, which automatically executes all benchmarks on SpiNNaker, BrainScaleS and NEST on a regular basis (Figure 3).

#### Progress vs State of the Art & Recent Developments

Benchmarking of neuromorphic hardware is a hot topic (for example, see the comment by Intel's Mike Davies in Nature Machine Intelligence, 2019). To our knowledge, SNABSuite is the only framework that incorporates several benchmarks and covers several hardware systems at the same time. Of a similar nature is the current endeavour to simulate the full-scale cortical microcircuit model on SpiNNaker, NEST, and GeNN, which is reported in several publications. However, these use platform-specific implementations, which is contrary to our approach.

Figure 3: Benchmark work-flow: from an application to the tracking of results in the web-service.

| Component | Link to                 | URL                                                              |  |  |

|-----------|-------------------------|------------------------------------------------------------------|--|--|

|           | Software Repository     | https://github.com/hbp-unibi/snabsuite                           |  |  |

| C2735 -   | Technical Documentation | https://hbp-unibi.github.io/SNABSuite/index.html                 |  |  |

| SNABSuite | User Documentation      | https://github.com/hbp-<br>unibi/SNABSuite/blob/master/README.md |  |  |

#### 4.1.7 Output 6: MUSIC library

The MUSIC communication framework enables modular development of neuronal network models and tools, and supports integration of neuromorphic hardware with HPC and neurorobotic hardware.

During the second half of SGA2, a new version of the MUSIC main development line was released (v1.1.16). This release partly serves as a reference point for current MUSIC users, but also as a preparation for an upcoming new release series supporting multiple communication algorithms (v2). In addition, a first version of MUSIC with a novel API, supporting user-requested features such as dynamic ports, has been released (v3.1.0) The two development lines (v1-2 and v3) will run in parallel, until the novel API has gained acceptance in the community.

| Component | Link to                 | URL                                                       |  |

|-----------|-------------------------|-----------------------------------------------------------|--|

| C347 SP9  | Software Repository     | https://github.com/INCF/MUSIC                             |  |

| MUSIC     | Technical Documentation | https://github.com/INCF/MUSIC/wiki/files/music-manual.pdf |  |

| library   | User Documentation      | https://github.com/INCF/MUSIC/wiki                        |  |

#### 4.1.8 Output 7: Hardware integration

The MUSIC SpiNNaker-adapters are software components which allow any MUSIC-aware software to interface with SpiNNaker.

During the second half of SGA2, the MUSIC SpiNNaker-adapters were improved and bugs fixed. Additional examples of their use have been written.

| Component               | Link to                 | URL                                                                        |

|-------------------------|-------------------------|----------------------------------------------------------------------------|

| C1810 -                 | Software Repository     | https://github.com/incf-music/spinnaker-adapters                           |

| MUSIC -                 | Technical Documentation |                                                                            |

| hardware<br>integration |                         | https://github.com/incf-music/spinnaker-<br>adapters/blob/master/README.md |

### 4.1.9 Output 8: CSA library

CSA (Connection-set algebra) is a formalism for expressing neuronal network connectivity. Novel connectivity patterns can be constructed in an abstract manner from basic patterns, using operators in a way that allows for efficient parallel instantiation of connections. A demonstration implementation in Python exists (<u>https://github.com/INCF/csa</u>). During the second half of SGA2, the novel C++ implementation was finalised and released (v1.0.0) and three releases of the Python implementation were made (v1.1.8, v1.1.10, v1.1.12).

| Component                  | Link to                 | URL                            |

|----------------------------|-------------------------|--------------------------------|

|                            | Software Repository     | https://github.com/INCF/libcsa |

| Connection-<br>set algebra | Technical Documentation |                                |

| library                    | User Documentation      |                                |

#### 4.1.10 Output 9: BrainScaleS-1 Software

The operating system (Müller *et al.* 2020a) was continuously developed, including the addition of new features, user wishes and bug fixes. Among these, the following improvements were put in place:

• HICANN chips on a wafer can be influenced by neighbouring chips when they are in an undefined state. To guarantee no mutual influence, an automated initialisation was added to the SLURM resource allocation mechanism. When requesting HICANNs, neighbouring chips are identified and

a database checked to see if they are already in a defined state. If not, they are initialised and marked in the database to shorten setup times of following runs.

- A feature was added that retries to initialise the on-wafer bus network, based on verification measurements from on-chip test features.

- A configuration mode was added that allows the HICANNs to be configured incrementally, without user interaction. The automated configuration tracks the configured state and re-configures only the components with settings that were changed between two executions. This allows faster and less error-prone iterative experiments.

| Component                     | Link to                 | URL                                                    |

|-------------------------------|-------------------------|--------------------------------------------------------|

|                               |                         | https://github.com/electronicvisions/                  |

| BrainScaleS-1<br>Neuromorphic | Technical Documentation | Integrated into code and internal specification        |

| Computing<br>System           |                         | https://electronicvisions.github.io/hbp-sp9-guidebook/ |

#### 4.1.11 Output 10: BrainScaleS-2 Software

In pursuit of the software specification in reference document <u>D9.2.1 - SGA2</u>, the following additions and developments were carried out (Müller *et al.* 2020b):

- The abstraction of the FPGA instruction set now fully implements write and read operations to and from all on-chip register types, the event communication and ADC response data, as well as FPGA SPI devices. Building and execution of a timed sequence of register-like write and read accesses, in the form of a "playback programme", is fully implemented. Event support, logging and printout improvements have been added to the now-complete transport-layer formatting library "hxcomm".

- Most full-custom chip configuration entities have been abstracted into corresponding container types, enabling configuration of: synapses, synapse drivers, neurons, readout-chains and routing, plasticity processor unit programme loading, execution control and result fetching, amongst other things.

- In addition, the implementation of containers in the logical configuration layer has been started. The array and matrix shape of configuration entities on the chip, e.g. the synapse matrix or parallel-column-ADC readout has been realised as alike container structures simplifying access. An "atomic" neuron container, embodying digital configuration alongside analogue parameters belonging to the said neuron, has been developed as a structured abstract representation.

- Verification of software changes was enhanced by an automation of the hardware simulation framework for the continuous integration workflow. Upload of a change to the code review service automatically triggers a build of the software suite and a startup of a hardware simulator instance. Software unit tests are automatically verified, connecting to the started simulator instance.

- The automatically generated C++-Python wrapper source code, as well as the Python-only parts of the interfaces, have been migrated from Python 2 to Python 3.

- In-code documentation of C++ sources using doxygen has been extended to almost full coverage in hxcomm, as well as fisch; it also covers the essential parts of the low-level configuration, logical configuration and experiment control layers (haldls, stadls and lola). Building the documentation is integrated in the build flow alongside of the shared library for C++ or Python libraries. For internal use, UHEI's Jenkins continuous integration server builds and deploys the documentation as a html-based website. Publishing this code documentation to the live "SP9 Guidebook" is work-in-progress.

- Extensions for the custom vector unit of the PowerPC-based plasticity processor unit have successfully been ported from gcc 4.9.4 to gcc 8.1, which acts as a full replacement. In addition, we now support the usage of "embedded" C++17.

| Component                     | Link to                 | URL                                                    |

|-------------------------------|-------------------------|--------------------------------------------------------|

|                               | Software Repositories   | https://github.com/electronicvisions/                  |

| BrainScaleS 2<br>Neuromorphic | Technical Documentation | D9.2.1, also in-code documentation                     |

| Computing<br>System           |                         | https://electronicvisions.github.io/hbp-sp9-guidebook/ |

## 4.2 Validation and Impact

#### 4.2.1 Actual and Potential Use of Output(s)

- **Output 1** (Multi-compartmental models in PyNN). This functionality is still in the early stages of development. As yet, we are not aware of any users. Within the HBP, the Arbor development team plans to implement support for the multi-compartment PyNN API during SGA3.

- Output 2 The SpiNNaker software is deployed as discussed in KR1. In addition to this, the software integration tests are run before any major changes are integrated into the main software, with these and some additional longer-running tests based on various user-provided scripts being run on a daily basis. This ensures that any breaking changes to the software are detected early.

- **Output 3** (App for machine-learning with neuromorphic hardware). Development versions of the app have been used in introductory spiking neural network courses for master and PhD students. The current refined version of the app is considered stable enough for such controlled guided classroom scenarios on the order of 10-20 participants.

- Output 4 We tested the new SW library for the porting on SpiNNaker of a parallel DNA sequencematching algorithm implemented by using the MPI programming paradigm. In the test, all cores of the board are configured for executing in parallel an optimised version of the Boyer-Moore (BM) algorithm. Exploiting this application, we benchmarked the SpiNNaker platform in terms of scalability and synchronisation latency. Experimental results indicate that the SpiNNaker parallel architecture allows a linear performance increase with the number of used cores and shows better scalability than a general-purpose, multi-core computing platform (Urgese *et al.*, 2019).

- **Output 5** (Neuromorphic Benchmarks). With the increasing interest in benchmarks, we expect a growing number of users for the web-service, which is tracking benchmark results. It requires and uses the full tool-chain of the SP9 infrastructure, and contributes in form of the aforementioned web-service.

- **Output 6** (MUSIC). MUSIC has been used as a middleware in the SPORE NEST module for studying synaptic plasticity with online reinforcement learning since 2017 (Kaiser *et al.*, 2019, Kappel *et al.*, 2018) as well as interfacing neuronal simulators to ROS (Weidel *et al.*, 2016, Bahaguna *et al.* 2018) and the OpenAI gym (Jordan *et al.*, 2017).

- **Output 7** (Hardware integration) A demonstrator application interfacing SpiNNaker with robotic hardware, using MUSIC SpiNNaker-adapters, is being developed.

- **Output 8** (CSA) CSA is used in the HBP Neurorobotics Platform (NRP) and has been used as an intermediate language in the generation of neuronal network connectivity from visual representations (Herbers, 2017).

- Output 9 (BSS-1) and Output 10 (BSS-2): The developments and added features for both BSS-1 and BSS-2 operating systems are used by all users of the neuromorphic hardware, especially the experiments carried out and described in KR 9.3.

#### 4.2.2 Publications

- Brocke, Ekaterina. "Method development for co-simulation of electrical-chemical systems in Neuroscience." Doctoral thesis <u>TRITA-EECS-AVL</u>; <u>2020:9</u>, KTH Stockholm. (Output 6, P2398) Relevance: the thesis describes an extension of MUSIC towards multiscale co-simulatio

- Urgese, Gianvito, Francesco Barchi, Emanuele Parisi, Evelina Forno, Andrea Acquaviva, and Enrico Macii. "Benchmarking a Many-Core Neuromorphic Platform with an MPI-Based DNA Sequence Matching Algorithm." Electronics 8, no. 11 (2019): 1342, DOI 10.3390/electronics8111342. (Output 4, P2286)

- Oliver Rhodes, Luca Peres, Andrew G. D. Rowley, Andrew Gait, Luis A. Plana, Christian Brenninkmeijer and Steve B. Furber. "Real-time cortical simulation on neuromorphic hardware". Philos Trans A Math Phys Eng Sci. 2020 Feb 7;378(2164):20190160. DOI:<u>10.1098/rsta.2019.0160</u> (Output 2, P2299)

- Ostrau, Christoph, Christian Klarhorst, Michael Thies, and Ulrich Rückert. "Comparing Neuromorphic Systems by Solving Sudoku Problems." In Conference Proceedings: 2019 International Conference on High Performance Computing & Simulation (HPCS). 2019. (Output 5, P2047)

- Eric Müller, Sebastian Schmitt, Christian Mauch, Sebastian Billaudelle, Andreas Grübl, Maurice Güttler, Dan Husmann, Joscha Ilmberger, Sebastian Jeltsch, Jakob Kaiser, Johann Klähn, Mitja Kleider, Christoph Koke, José Montes, Paul Müller, Johannes Partzsch, Felix Passenberg, Hartmut Schmidt, Bernhard Vogginger, Jonas Weidner, Christian Mayr, Johannes Schemmel "The Operating System of the Neuromorphic BrainScaleS-1 System", 2020a, arXiv 2003.13749 (Output 9, P2490)

- Eric Müller, Christian Mauch, Philipp Spilger, Oliver Julien Breitwieser, Johann Klähn, David Stöckel, Timo Wunderlich, Johannes Schemmel "Extending BrainScaleS OS for BrainScaleS-2", 2020b, arXiv 2003.13750 (Output 10, P2491)

# 5. Key Result KR9.3: Operational prototype of a 2<sup>nd</sup> generation BrainScaleS chip featuring on-chip local plasticity and non-linear dendritic processing

## 5.1 Outputs

#### 5.1.1 Overview of Outputs

#### 5.1.1.1 List of Outputs contributing to this KR

- Output 1: Deep learning with time-to-first-spike coding

- Output 2: Sampling-based Bayesian computation

- Output 3: Structural plasticity

- Output 4: Control of criticality and computation

- Output 5: Insect-inspired navigation

- Output 6: Spiking Heidelberg Digits

- Output 7: BrainScaleS-2 setups

#### 5.1.1.2 How Outputs relate to each other and the Key Result

The research/tests described here make use of the BrainScaleS-2 chips [Schemmel, 2020] and serve as validation of the manufactured hardware systems and the necessary software environment.

| Component Link to                |                            | URL                                                                                                            |  |

|----------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------|--|

| C0457: SP9 BrainScaleS 2         | Technical<br>Documentation | Starting to appear at:<br><u>https://electronicvisions.github.io/hbp-sp9-</u><br><u>guidebook/pm/bss2.html</u> |  |

| Neuromorphic Computing<br>System | User Documentation         | Starting to appear at:<br><u>https://electronicvisions.github.io/hbp-sp9-</u><br>guidebook/pm/bss2.html        |  |

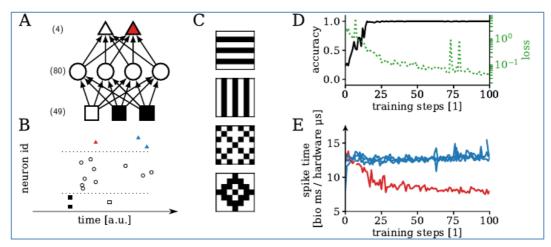

## 5.1.2 Output 1: Deep learning with time-to-first-spike coding

Figure 4: Feed-forward network for fast inference

For fast inference, we train a feed-forward network (Figure 4A) that uses time-to-first-spike coding, for both input and classification (B). We analytically derived differentiable equations for the spike time of leaky integrate-and-fire neurons [Goeltz, 2019] that provide learning rules based on error-backpropagation. On a sample data set (C) with inference on BrainScaleS-2 and update calculation on a host, training succeeds fast (D) and neurons coding correct classes (E, red) decrease their spike time compared to wrong classes (blue). The speed of inference (about 10µs per pattern) is independent of emulated network size, classification of larger data sets is work in progress.

#### 5.1.3 Output 2: Sampling-based Bayesian computation

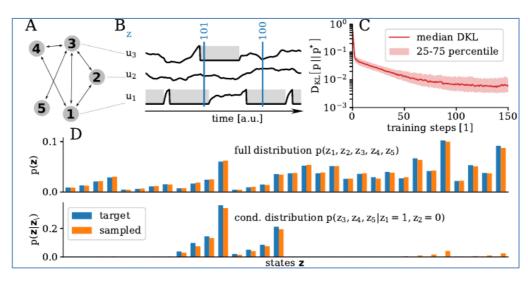

#### Figure 5: Network of LIF neurons for Bayesian inference

Networks of LIF neurons can perform Bayesian inference through sampling on probability distributions defined over binary variables [Petrovici, 2016]: During post-spike refractoriness, a neuron is considered to be in the state z=1, and z=0 otherwise (Figure 5A,B). We used contrastive Hebbian learning with updates calculated on a host PC, and monitor the Kullback-Leibler divergence to the target distribution (C) [Billaudelle, 2019b]. After training, the network reliably performed Bayesian inference on its target distribution (D).

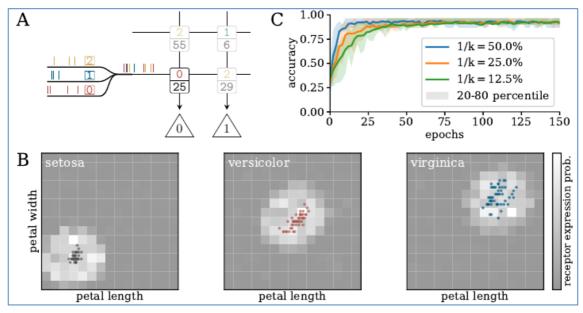

#### 5.1.4 Output 3: Structural plasticity

Figure 6: Structural plasticity on BrainScaleS-2

We utilise the event routing scheme inherent in the BrainScaleS-2 architecture (Figure 6A) to efficiently implement structural plasticity [Billaudelle, 2019a]. During learning, the connectome emerges from a pool of potential connections. The synaptic fan-in of a neuron is kept constant over time, resulting in a sparse connectivity structure. Our structural plasticity algorithm leads to the formation of receptive fields closely resembling the topology of the data set (B). It converges to an optimal classification performance independent of the imposed sparsity level (C), here for the Iris data set.

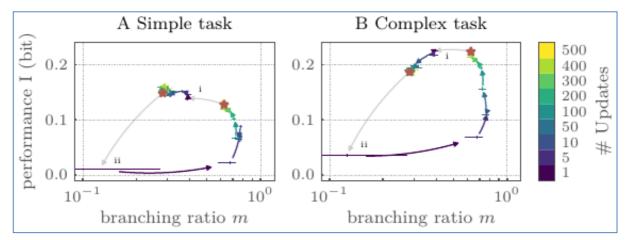

#### 5.1.5 Output 4: Control of criticality and computation

We developed a spiking network with on-chip synaptic plasticity for which the distance to criticality can be easily adapted by changing the input strength [Cramer, 2019a]. With this setup, we then demonstrate a clear relation between criticality, task-performance and information-theoretic fingerprint. The critical state is assumed to be optimal for any computation in recurrent neural networks, because criticality maximizes a number of abstract computational properties. Whereas the information-theoretic measures all show that network capacity is maximal at criticality, this is not the case for performance on specific tasks: Only the complex, memory-intensive tasks profits from criticality (Figure 7B), whereas the simple tasks suffer from it (A). Thereby, we challenge the general assumption that criticality would be beneficial for any task, and provide instead an understanding of how the collective network state should be tuned to task requirement to achieve optimal performance.

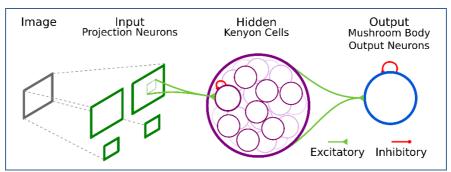

#### 5.1.6 Output 5: Insect-inspired navigation

Figure 8: Virtual insectoid agent on BrainScaleS-2

A virtual insectoid agent on BrainScaleS-2 uses path integration to navigate back home after spreading out randomly [Billaudelle, 2019b]. The network is schematically depicted next to the activity histogram (Figure 8A). Information flows from the sensory layer at the top through an integration and a steering layer to the motor neurons at the bottom. A typical trajectory of the virtual insect which turns to random looping around the home position upon reaching it is shown in (B). (C) shows an overlay of 100 trajectories like that, each with a different random outbound journey.

#### 5.1.7 Output 6: Spiking Heidelberg Digits

Figure 9: Representation of the Spoken digits dataset

Spiking neural networks are the basis of versatile and power-efficient information processing in the brain. To accelerate the development of spiking neural network models, objective ways to compare their performance are indispensable. Presently, however, there are no widely accepted means for comparing the computational performance of spiking neural networks. To address this issue, we introduce a general audio-to-spiking conversion procedure and provide two novel spike-based classification datasets [Cramer 2019b, Figure 9]. The datasets are free and require no additional pre-processing, which renders them broadly applicable to benchmark both software and neuromorphic hardware implementations of spiking neural networks.

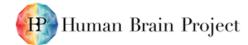

### 5.1.8 Output 7: BrainScaleS-2 setups

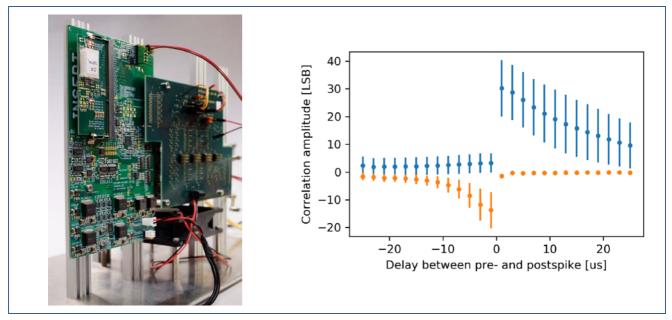

Figure 10: BrainScaleS-2 HICANN-X setup

We developed new HICANN-X setups which can readily be used for experiments. Fourteen of them are already located in our laboratory. First experiments have been successful. In Figure 10, next to the photo of one of the setups, the synapses' correlation sensors are characterised. The plot shows means and standard deviations of all 32,768 synapses which are located in one quadrant of the chip. The timing of pre- and postsynaptic spikes is measured in every synapse. If presynaptic events are

followed by postsynaptic ones, these positive delays result in causal amplitudes (blue); the inverse order implies anti-causal correlation (orange). These correlations can be processed making use of the local microprocessor, allowing for weight updates and on-chip learning based on spike-timing dependent plasticity (STDP).

## 5.2 Validation and Impact

### 5.2.1 Actual and Potential Use of Output(s)

The outputs are first test- and demonstration uses of the Key Result (the chip + system) and at the same time show some of the potential of the systems. The exploitation of the BrainScaleS-2 single-chip (and then also multi-chip) systems for research and, potentially, industrial use is planned for SGA3. The BrainScaleS-2 chips/systems developed and tested in SGA2 will become part of the EBRAINS platform in SGA3.

#### 5.2.2 Publications

- [Billaudelle, 2019a] S. Billaudelle, B. Cramer, M. A. Petrovici, K. Schreiber, D. Kappel, J. Schemmel, and K. Meier, "Structural plasticity on an accelerated analog neuromorphic hardware system" arXiv preprint arXiv:<u>1912.12047</u>, 2019 (Output3, P2240)